# BLOQUES DE ADAPTACIÓN ANALÓGICOS BASADOS EN LMS DE SIGNO

## Edgar López Delgadillo

Universidad Autónoma de Aguascalientes elopezd @correo.uaa.mx

## Luis Alejandro Flores Oropeza

Universidad Autónoma de Aguascalientes

##Iores@correo.uaa.mx

## Alejandro Díaz Méndez

Universidad Autónoma de Aguascalientes ajdiaz@inaoep.mx.

#### Resumen

En años recientes los sistemas adaptivos se han convertido en un tema importante para distintas aplicaciones. En particular, los sistemas adaptivos analógicos son importantes cuando se requiere una razón de convergencia rápida o cuando las señales procesadas tienen un ancho de banda amplio. En este artículo se presenta la implementación de un sistema adaptivo analógico basado en el criterio LMS de signo y considerando un tamaño de paso variable. El desempeño del sistema propuesto se demuestra mediante simulaciones usando modelos en VerilogA y a nivel transistor en tecnología CMOS.

Palabra(s) Clave(s): Filtro adaptivo, paso variable, SS-LMS.

## 1. Introducción

En años recientes los sistemas adaptivos analógicos se han convertido en un tema importante de investigación para su aplicación en diversas áreas tales como comunicaciones, sistemas de audio, control entre otras. Aunado a esto, en aplicaciones "on chip" las variaciones de proceso, temperatura y voltaje pueden

resultar en un mal funcionamiento de los circuitos. Para solucionar este problema se han implementado diversas técnicas adaptivas dentro del circuito integrado de tal manera que las variaciones mencionadas no afecten al sistema.

En aplicaciones comunes los sistemas adaptables se implementan generalmente en el dominio digital debido a que las operaciones matemáticas que requieren son fácilmente implementadas de esta manera. Sin embargo, hay aplicaciones en las cuales el ancho de banda de las señales que se procesan y las velocidades de convergencia requeridas son tan altas que los sistemas adaptables digitales tradicionales resultan de poca utilidad. En este caso se pueden implementar las técnicas adaptivas analógicas para solucionar los problemas mencionados.

Tanto en el dominio analógico como en el digital, una de las técnicas más utilizadas para adaptar los sistemas, en particular filtros, es el criterio LMS (Least Mean Squares). Esto debido a su simplicidad matemática comparado con otras técnicas como RLS (Recursive Least Squares). Desafortunadamente a pesar de la simplicidad de LMS, cuando se implementa en aplicaciones dentro de chip puede ocupar grandes cantidades de área debido a la necesidad de operaciones de multiplicación e integración en su implementación.

Debido a las razones expuestas anteriormente existe la necesidad de proponer estructuras adaptivas analógicas con un número reducido de elementos de circuito y con una velocidad de convergencia alta para aplicaciones en circuitos integrados CMOS.

En [1] y [3] se presentan los desarrollos más representativos en lo referente a los filtros adaptivos analógicos incluyendo sus ventajas y desventajas. En ambos casos se presenta la formulación matemática y diagramas de bloques pero no se llega a una implementación concreta. En [2] se analiza el desempeño en DC de cuatro filtros adaptables analógicos, incluyendo entre ellos las realizaciones con signo del criterio LMS. En [5] se propone la implementación de un filtro analógico LMS en una tecnología CMOS estándar. Para este último una de las principales características es la gran cantidad de área en silicio que requiere. En [6,7] presentamos una solución que requiere una menor área de silicio, a diferencia de implementaciones anteriores.

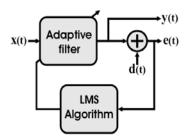

## 2. Filtros Adaptivos Analógicos

En la figura 1 se presenta la estructura general de un filtro adaptivo analógico. Este sistema tiene dos bloques principales, el primero es el filtro adaptable que se caracteriza por la posibilidad de programas algunos de sus parámetros. El segundo bloque corresponde al criterio de adaptación el cual se usa para modificar los parámetros del filtro. Las entradas al sistema son: la señal a ser filtrada x(t) la señal deseada d(t).Las salidas son la señal de error e(t) y la filtrada y(t). El objetivo del sistema es adaptar los parámetros de tal manera que el error sea lo más pequeño posible.

Figura 1 Estructura general de un filtro adaptivo analógico.

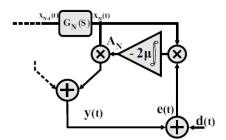

Una de las realizaciones de filtros adaptables más utilizadas es la transversal. Sus principales ventajas son la simplicidad, la estabilidad y la disponibilidad de algoritmos para adaptar sus parámetros. En particular, una estructura de este tipo de filtros se presenta en la figura 2, [1,3], la cual está integrada por la conexión en cascada de funciones  $G_i(S)$  las cuales típicamente se implementan mediante estructuras de Laguerre o Gamma. La salida y(t) del sistema es la combinación lineal de las señales  $X_i$ , mientras que los pesos  $A_i$  pueden ser establecidos dinámicamente de manera que se tenga una señal de error lo más pequeña posible.

Figura 2 Estructura transversal de un filtro adaptivo analógico.

El algoritmo LMS ha sido ampliamente utilizado en filtrado adaptivo, en particular en estructuras transversales, debido a su simplicidad comparado con otras técnicas. La expresión en tiempo continuo para la adaptación con este criterio se muestra en la ecuación 1. Esta se obtiene de su contraparte en tiempo discreto haciendo una aproximación a cero del tiempo de muestreo.

$$A_{i}(t) = -2\mu \int_{-\infty}^{t} e(u) \nabla_{Ai}(e(u)) du$$

(1)

A partir de la ecuación 1 se obtiene el diagrama a bloques de una de las etapas de adaptación del tipo LMS en tiempo continuo tal como se muestra en figura 3. Como se aprecia, se requiere al menos un integrador, un multiplicador y una etapa de ganancia para cada uno de los pesos  $A_i$  del filtro. En consecuencia, a mayor tamaño del filtro transversal, mayor es el número de elementos de circuito analógico necesarios para adaptarlo.

Figura 3 Estructura LMS analógica.

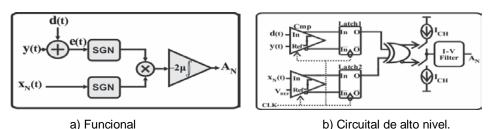

Una alternativa que reduce el número de operaciones y por ende el número de elementos de circuito del LMS es el SS-LMS (Sign-Sign LMS). En este sistema solo se consideran los signos del error y del gradiente del error tal como se muestra en ecuación 2.

$$A_{i}(t) = -2\mu \int_{-\infty}^{t} \operatorname{sgn}(e(u)) \operatorname{sgn}(\nabla_{Ai}(e(u))) du$$

(2)

En la ecuación 2, debido al uso de las funciones signo, la multiplicación resulta en una operación trivial de dos niveles lógicos que se puede realizar mediante una compuerta XOR. En consecuencia la integración también es una operación trivial.

La desventaja de un algoritmo basado en signo es que tiene un exceso de MSE mayor al del criterio LMS tradicional. Aún más, su proceso de convergencia es más lento. A pesar de esto se puede establecer un buen compromiso entre velocidad y precisión en términos de la constante  $\mu$ . Finalmente las condiciones de estabilidad para este tipo de filtros se establecen en [7] y [8].

# 3. Filtro SS-LMS propuesto

La metodología de diseño que se ha considerado para el desarrollo de este trabajo es llamada "Top-Down" y es utilizada en el diseño de circuitos integrados para asegurar el funcionamiento correcto de bloques de circuito y para establecer condiciones de diseño para éstos en tecnología CMOS. Los pasos de la metodología son los siguientes:

- 1. Definición funcional de estructuras de alto nivel.

- 2. Definición de circuitos de alto nivel (funcionamiento general de bloques de circuito).

- Diseño a nivel transistor de cada bloque de circuitos en una tecnología CMOS estándar.

- Desarrollo de los patrones geométricos (Layout) para cada bloque de circuitos diseñado.

- 5. Fabricación del circuito integrado.

Después de cada uno de los pasos anteriores existe una etapa de pruebas y validación. Para los pasos 1 al 4, estas pruebas se realizan mediante simulaciones, por lo que los materiales son los programas de simulación. Por otro lado, el paso 5 se valida con la implementación física del circuito integrado diseñado, en consecuencia los materiales son el equipo de laboratorio de electrónica y el prototipo de circuito integrado. Es importante mencionar que para el presente artículo se consideran resultados y pruebas de los puntos 1 al 3.

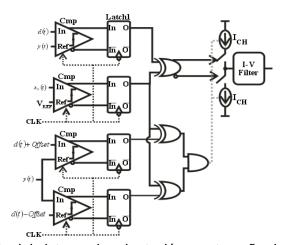

Una de las estructuras adaptables que se desarrollan se basa en la ecuación 2. Los modelos para los puntos uno y dos de la metodología se muestran en la figura 4. Las funciones signo se implementan mediante comparadores temporizados y la integración es realizada por una bomba de carga y un filtro, mientras que la multiplicación de los signos se realiza mediante una compuerta XOR.

Figura 4 Modelos del sistema de adaptación.

Otra de las estructuras adaptables desarrolladas es la que se muestra en la figura 5. Esta es similar a la presentada en la figura 4b, solo se agrega una estructura basada en elementos similares a los del circuito original. Dicha estructura funciona como un comparador de ventana y tiene por objetivo permitir un paso variable en el tiempo de adaptación, de manera que esta sea rápida y precisa al mismo tiempo.

Figura 5 Modelo del sistema de adaptación con tamaño de paso variable.

Los modelos funcionales y circuitales de alto nivel de la figuras 4 y 5 se implementan con la ayuda del lenguaje de descripción VerilogA (Verilog analógico), de manera que es posible obtener un prototipo en corto tiempo para verificar funcionalidad y condiciones de diseño.

Un ejemplo del desarrollo de modelos mediante VerilogA se muestra en la figura 6, donde se aprecia el bloque de comparación temporizada. Como se observa en la figura 5(a) el modelado es muy sencillo, sin embargo se pueden tomar en cuenta fenómenos no ideales como la histéresis, retardos, tiempos de ascenso y descenso de la señal de salida, etc.

Figura 6 Prototipo del comparador en VerilogA.

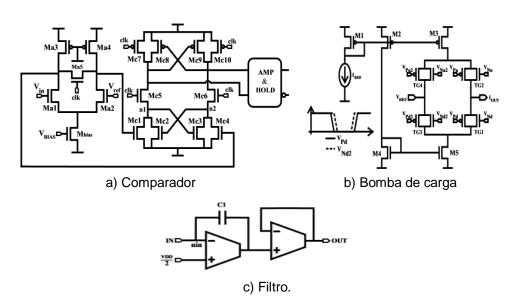

Para el diseño a nivel transistor del bloque de adaptación se considera una tecnología CMOS 0.35um de Austria Microsystems y las simulaciones se han realizado con las herramientas de Mentor Graphics. En la figura 7 se muestran los circuitos implementados para el comparador (figura 7a), la bomba de carga (figura 7b) y el filtro (figura 7c). Cabe mencionar que los OTAS utilizados en el filtro se realizan mediante una estructura diferencial simple.

Figura 7 Diseño transistor tecnología CMOS para los bloques del sistema de adaptación.

## 4. Resultados y Discusión

Para verificar el desempeño del sistema de adaptación basado en el esquema SS-LMS se considera una señal deseada d(t) constante y una retroalimentación entre salida y entrada de manera que la salida del sistema sea capaz de adquirir el valor de la señal deseada. La métrica de desempeño utilizada es el error normalizado expresado en dB.

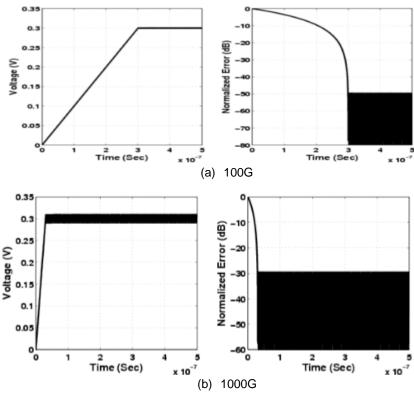

En la figura 8 se presentan los resultados de simulación del sistema de adaptación de la figura 4 utilizando los modelos en VerilogA para dos valores distintos de ganancia del sistema. Cabe mencionar que dicha ganancia se establece mediante el valor de la corriente de la bomba de carga y el valor del capacitor en el filtro. En la figura se aprecia la señal de salida y la de error normalizada y expresada en dB. Es claro que cuando se incrementa la ganancia se disminuye el tiempo de adaptación, sin embargo el piso de ruido se incrementa. Por este motivo es necesario mantener un compromiso entre rapidez y precisión en función de la ganancia.

Figura 8 Resultados de simulación con modelos en VerilogA y ganancias.

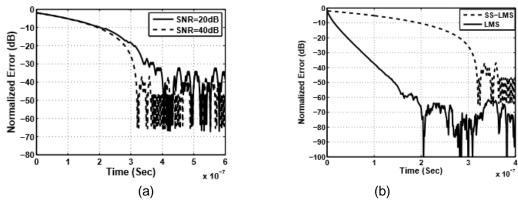

En la figura 9a se muestra el comportamiento del sistema en presencia de ruido para 20 y 40 dB de relación señal a ruido (SNR). Resulta evidente que el valor del piso de ruido es proporcional a la SNR. En la figura 9b se presenta una comparación entre la estructura propuesta y un LMS convencional. Este último también es modelado en VerilogA. Aunque el desempeño de la estructura propuesta es menor que la LMS, SS-LMS presenta cantidad reducida de elementos de circuito.

Figura 9 a) Efectos del ruidoy b) Comparación LMS Vs SS-LMS.

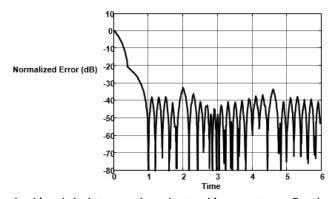

En la figura 10 se muestran los resultados de simulación del sistema de adaptación con tamaño de paso variable. En esta se puede apreciar que el piso de ruido alcanzado es pequeño, sin embargo el tiempo de adaptación se mantiene considerablemente corto.

Figura 10 Simulación del sistema de adaptación con tamaño de paso variable.

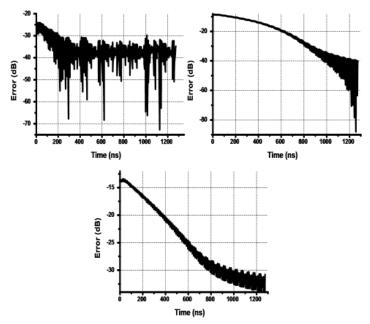

Finalmente, los resultados de simulación con los circuitos CMOS se exhiben en la figura 11. Para las simulaciones se utilizan los modelos del fabricante para los

transistores MOS. En particular para los resultados presentados se utilizan los modelos de esquinas ("worst cases"). En todos los casos el piso de ruido está por debajo de -30 dB.

Figura 11 Resultados de simulación a nivel transistor.

## 5. Conclusiones

Se ha presentado un sistema de adaptación basado en SS-LMS. Su implementación representa una reducción de elementos de circuito comparado con el LMS. El uso de comparadores temporizados permite que la señal tratada tenga una frecuencia mayor que la del reloj del sistema. Se ha probado mediante simulaciones de alto nivel con modelos en verilog A que la magnitud del error es directamente proporcional a la ganancia del sistema.

También se ha mostrado que el tiempo de convergencia es inversamente proporcional a la ganancia del sistema. Para cada uno de los bloques del sistema se ha diseñado su circuito correspondiente en una tecnología CMOS estándar.

# 6. Bibliografía y Referencias

[1] Carusone, D. Johns, "Analog adaptive filters: Past and present". IEEE Proceedings Circuits, Devices and Systems. Vol. 1 No. 174. Feb. 2000. Pp. 82-90.

- [2] Shoval, "DC offset performance of four LMS adaptive algorithms". IEEE International Sympoisum on Circuits and Systems. 1994. Pp. 409-412.

- [3] H. A Perez-Meana, "Survey of Aadaptive Analog Filter". journal Telecommunications and Radio Engineering. Vol. 6. No. 56. 2001

- [4] D. Johns, K. Martin, Analog Integrated Circuit Design. 1997. John Wiley and Sons, Inc.

- [5] Muer, CMOS Fractional-N Synthesizers. 2003. Kluer Academics Publishers.

- [6] J. A. Díaz-Méndez, M. A. García-Andrade, M. E. Magaña, F. Maloberti, 52nd IEEE International Midwest Symposium on Circuits and Systems, DOI: 10.1109/MWSCAS.2009.5236143. 2-5 Aug. 2009.

- [7] E. López-Delgadillo, J. A. Díaz-Méndez, M. A. García-Andrade, "Circuits Syst Signal Process". Doi:10.1007/s00034-014-9821-6. Vol. 33. 2014. Pp. 3331.

## 7. Autores

Edgar López Delgadillo. Graduado de Ingeniería en Electrónica y Sistemas de Comunicación Digital por la Universidad Autónoma de Aguascalientes en 2002. Obtuvo los grados de Maestro en Ciencias y Doctor en Ciencias por el Instituto Nacional de Astrofísica, Óptica y Electrónica en 2004 y 2010 respectivamente. Actualmente es profesor investigador titular adscrito al Centro de Ciencias Básicas de la Universidad Autónoma de Aguascalientes. Sus principales áreas de interés son el diseño de circuitos integrados analógicos y en modo mixto y los sistemas adaptables digitales y analógicos.

Luis Alejandro Flores Oropeza nació en Aguascalientes, México en 1976, obtuvo el título de Ingeniero Eléctrico por parte del Instituto Tecnológico de Aguascalientes y el grado de Doctor en Ingeniería Electrónica por la Universidad Politécnica de Madrid en España en 1999 y 2005 respectivamente. Actualmente es profesor investigador de tiempo completo en la Universidad Autónoma de Aguascalientes. Sus intereses se centran en el estudio de las fuentes de alimentación conmutadas, corrección del factor de potencia y control.